![基于VHDL的FPGA和NiosII实例精炼 《基于VHDL的FPGA和NiosII实例精炼》[44M]百度网盘|pdf下载|亲测有效](/365baixing/uploads/s0309/8b70ddc3-e6a7-4072-a033-ad9e68618a61.jpg)

![《基于VHDL的FPGA和NiosII实例精炼》[44M]百度网盘|pdf下载|亲测有效](/365baixing/uploads/s0309/8b70ddc3-e6a7-4072-a033-ad9e68618a61.jpg)

基于VHDL的FPGA和NiosII实例精炼 pdf下载

8.99¥

10.99¥

内容简介

本篇主要提供基于VHDL的FPGA和NiosII实例精炼电子书的pdf版本下载,本电子书下载方式为百度网盘方式,点击以上按钮下单完成后即会通过邮件和网页的方式发货,有问题请联系邮箱ebook666@outlook.com

编辑推荐

《基于VHDL的FPGA和Nios II实例精炼》是工程师经验手记。整章QuanusⅡ基本操作,无师自通;

90个VHDL知识点,个个击破;

13个基础实例,快速入门;

5个实用设计,开卷有益;

6个Nios Ⅱ基本组件,详细讲解;

2个Nios Ⅱ综合应用,步步说明;

22个视频教程以及所有实例的源代码配合《基于VHDL的FPGA和Nios II实例精炼》,让VHDL、FPGA、Nios Ⅱ

学习更加轻松自如。

90个VHDL知识点,个个击破;

13个基础实例,快速入门;

5个实用设计,开卷有益;

6个Nios Ⅱ基本组件,详细讲解;

2个Nios Ⅱ综合应用,步步说明;

22个视频教程以及所有实例的源代码配合《基于VHDL的FPGA和Nios II实例精炼》,让VHDL、FPGA、Nios Ⅱ

学习更加轻松自如。

内容简介

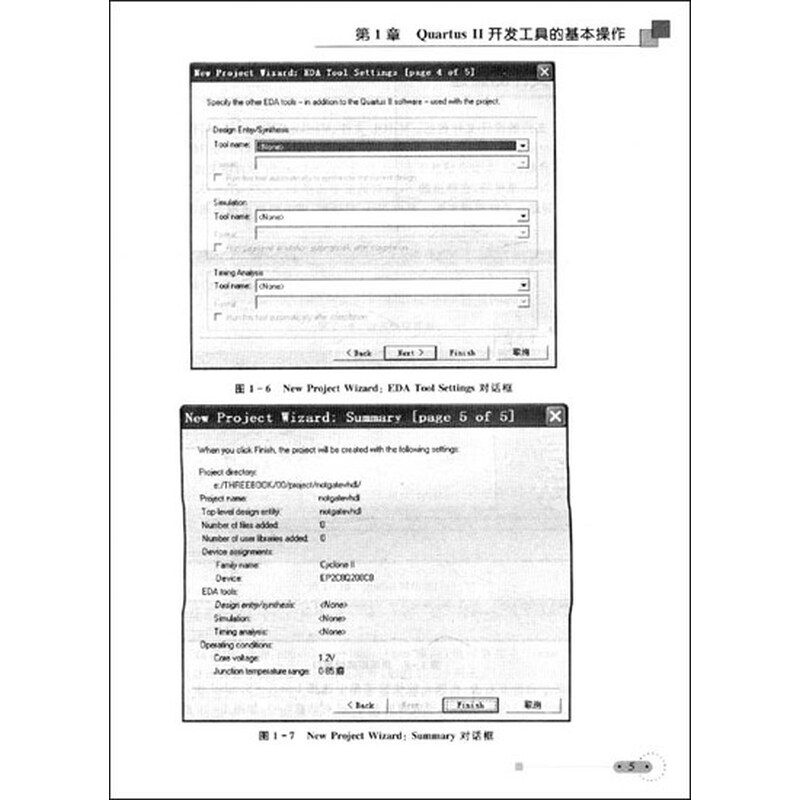

《基于VHDL的FPGA和Nios II实例精炼》分为4个部分:Quartus Ⅱ软件的基本操作、VHDL语法介绍、FPGA设计实例和Nios Ⅱ设计实例。首先介绍了Quartus Ⅱ的基本操作,包括工程的新建、代码的编辑、原理图的设计、VHDL代码设计、仿真及FPGA配置文件的下载等FPGA的设计。之后详细介绍了VHDL的基本语法,且配合VHDL程序实例以一个一个VHDL知识点的方式介绍,让读者从复杂的VHDL语法中解脱出来。然后,以实例为切入点,从简单到复杂,介绍了组合电路的建模、时序电路的建模、综合实例的设计。接下来在Nios Ⅱ的讲解中,《基于VHDL的FPGA和Nios II实例精炼》首先介绍了最小Nios II系统的搭建,并以多种使用方式介绍其自带的IP模块使用,包括PIO模块的应用、UART模块的应用、定时器模块的应用、DMA模块的应用;最后介绍两个实用型的Nios Ⅱ系统:基于DS18820的温度传感系统和基于PCF8563的时钟实时显示系统。

《基于VHDL的FPGA和NiosⅡ实例精炼》总结了编者几年来的FPGA设计经验,力求给初学者或是想接触这方面知识的读者提供一种快速入门的方法。《基于VHDL的FPGA和NiosⅡ实例精炼》适合电子相关专业的大学生、FPGA的初学者以及对FPGA有兴趣的电子工程师。

《基于VHDL的FPGA和NiosⅡ实例精炼》总结了编者几年来的FPGA设计经验,力求给初学者或是想接触这方面知识的读者提供一种快速入门的方法。《基于VHDL的FPGA和NiosⅡ实例精炼》适合电子相关专业的大学生、FPGA的初学者以及对FPGA有兴趣的电子工程师。

![《 2024新版 autocad 2024从入门到精通书籍 实战案例视频版 CADCAMCAE Auto CAD教材自学版》[65M]百度网盘|pdf下载|亲测有效](/365baixing/upload/2025-03-08/29623592-1_w_1698287571.jpg)

![《IT大趋势:—年全球信息技术导航图》[72M]百度网盘|pdf下载|亲测有效](/365baixing/uploads/s0309/58f72141Nede999be.jpg)

![《Android开发课堂实录课堂实录》[92M]百度网盘|pdf下载|亲测有效](/365baixing/uploads/s0309/56d7d61dNab9ecb2d.jpg)

![《 剪映专业版从新手到高手》[98M]百度网盘|pdf下载|亲测有效](/365baixing/upload/2025-03-08/29524475-1_w_1.jpg)